Frecuencias de Reloj y CPU

Esta página ha sido visitada

Frecuencia de Reloj, Microprocesador,

El MOS Technology 6502 es un microprocesador de 8 bits diseñado por MOS Technology en 1975. Cuando se introduce en el mercado es la CPU completa más barata de lejos, a 1/6 o menos del precio de sus competidoras los gigantes Intel y Motorola. Es además mucho más rápida, y con el Zilog Z80, serán el motor de numerosos desarrollos informáticos que devendrán en la revolución del ordenador doméstico de los 80. El diseño del 6502 es vendido a Rockwell y Synertek (MOS sigue fabricándolo) y licenciado más adelante a numerosas compañías. Todavía se usa en diseños embebidos.

Historia y uso

El 6502 es diseñado por el mismo equipo que creó el Motorola 6800. Tras abandonar Motorola en masa, diseñaron rápidamente el 6501, un nuevo diseño pero pin-compatible con el 6800. Motorola les demandado inmediatamente, y aunque el caso se habría solucionado por acuerdo, el daño a MOS es tan grave para que acuerden parar la producción del 6501.

El resultado es el "legalmente-compatible" 6502, que se diferencia sólo por un cambio del pinout que lo hace inutilizable en una placa base 6800; Motorola no parece más interesado. Sin embargo esto deja a MOS con el problema de conseguir nuevos desarrollos para el sistema, por lo que el ingeniero Chuck Peddle diseña el KIM-1, un ordenador monotarjeta. Para su sorpresa, el Kim-1 tiene ventas muy numerosas a los aficionados, así como al mercado previsto de ingenieros. El Rockwell AIM 65, un sistema de control/entrenamiento/desarrollo se vende también bien. Otr diseño similar es el Synertek Sym-1 .

El 6502 se lanza al mercado en Septiembre de 1975 a $25, mientras que los 6800 e Intel 8008 se vendían a $179. Al principio mucha gente pensaba que era algún tipo de engaño pero antes de que se monte una demostración, Motorola e Intel reducen sus precios a $79. En vez del ahorro, el 6502 estaba ahora legitimado y comenzaron a vender por centenares.

El 6502 tiene una característica que lo hace ideal para los sistemas de ordenadores domésticos, un pequeño retraso en el que se garantiza que no tiene acceso al bus. El hardware de video puede utilizar ese período para leer una línea de la pantalla sin tener que pausar el 6502 mientras esto ocurre. En términos generales esto acelera el funcionamiento de un sistema 6502 en un 25%.

Una de los primeros usos es la consola de videojuegos Atari 2600. La 2600 utilizan un vástago del 6502 llamado 6507, que tiene menos pines y por ello sólo puede direccionar 8 Kb de RAM. Se venderán millones. El siguiente uso del 6502 es la familia Apple II , y tras ello aparecen rápidamente varios ordenadores de Commodore, Atari, el BBC micro (y toda la serie atómica de Acorn), y un número enorme de otro diseños ahora perdidos en la historia.

Otro uso importante del 6502 es la Nintendo Famicom , una consola de videojuegos japonesa. Su equivalente norteamericano y europeo es la NES ( Nintendo Entertainment System ) El 6502 usado en la NES es una versión modificada que fue producida solamente para Nintendo, llamada 2A03. El 2A03 carece del modo decimal 6502 pero agrega 23 registros mapeados en memoria para generar sonido, dibujo de objetos, y la lectura del joypad.

El eficiente diseño de los 6502 también inspira a los diseñadores del procesador del RISC ARM, y así la herencia de los 6502 se puede de decir para superar al procesador original (familia) puesto que su espíritu vive en el diseño del ARM, usado en varias computadoras de escritorio así como en numerosos PDAs, ordenadores de mano, teléfonos móviles y sistemas embebidos, y se vende como un bloque IP que se usa en sistemas todo-en-un-chip.

Descripción

El 6502 es un procesador 8-bit con un bus de direcciones de 16-bits . La lógica interna funciona a la misma velocidad que la frecuencia del reloj externo, pero las velocidades de reloj aparentemente lentas, típicamente 1 Mhz , eran realmente competitivas con otras CPUs que funcionaban cuatro veces más rápidas porque es un procesador pipelined estáticamente, y los otros de su tiempo fueron microcodificados y tenían velocidades internas comparables con los 6502 (el reloj interno del Z80, por ejemplo, está dividido por cuatro). Aunque esto puede sonar como un truco, tenía el efecto secundario de reducir la velocidad requerida para los periférico unidos a la CPU, reduciendo así el coste total del sistema; un factor importante para producir diseños ganadores para elñ muy sensible mercado de las consolas y ordenadores domésticos.

A diferencia del Intel 8080 y microprocesadores similares, el 6502 tiene muy pocos registros. Cuando la RAM es más rápida que la CPU, tiene sentido optimizar el acceso a RAM más que aumentan el número de registros en un chip. Dentro hay un registro acumulador de 8 bits (A), dos registros de índice de 8 bits (X e Y), un registro de estado de 8 bits (SR), un puntero de pila de 8 bits (SP), y un contador de programa de 16 bits (PC). La subrutina call/scratchpad de la pila de direcciones está direccionada por hard a la página $01 , es decir el rango $0100 - $01FF ( 256 - 511 ) de la memoria. El acceso del software a la pila se hace mediante cuatro instrucciones de direccionamiento cuya función es poner o quitar el acumulador o el registro del estado del procesador.

El chip utiliza el índice y los registros de pila con eficacia con varios modos de direccionamiento, incluyendo un rápido "página directa" o modo "página cero" que accede a las posiciones de memoria las posiciones de memoria de la dirección 0 a 255 con una sola dirección de 8 bits (no necesita traer un segundo octeto para la dirección) El código para el 6502 utiliza la página cero mucho pues el código para otros procesadores hubiera utilizado los registros. Por razones obvias, en la mayoría de los microordenadores basados en 6502 con un sistema operativo el OS en sí mismo casi utiliza la página cero entera, dejando apenas un puñado de las direcciones para el usuario.

Modos de dirección también incluyen implicados (instrucciones de 1 octeto); absoluto (3 octetos); relativo (2 octetos); acumulador (1); indirecto, x e indirecto, y (2); e inmediato (2). El modo absoluto era un modo de uso general. Relativo es usado para los saltos de rama condicionales, que pueden mover el contador de programa hasta 128 octetos adelante o atrás. El modo del acumulador utiliza el acumulador como direccionamiento efectivo, y no necesita ningun dato de operando. El modo inmediato utiliza un operando literal 8-bit.

Los modos indirectos son útiles para procesar arrays y otros bucles. Con el modo indirecto, y el registro de 8 bits Y es añadido a una base de 16 bits situada en la pagina cero de la memoria (un byte en el opcode denota la localización de la página cero). Los registros de 8 bits X e Y son utilizados más como calificadores de desplazamiento que su uso ' normal ' de registros de índice. Incrementando X o Y para recorrer el array es una operación de dos ciclos de 8 bits, incluso si el array está situado en cualquier lugar de las direcciones de 16 bits (dado que la base 16-bits se lee en la página cero). Aquí es donde los 6502 se diferencian más del Motorola 6800. Un vistazo superficial a las especificaciones del 6502 que dicen que hay solamente registros de índice de 8 bits indice a error.

Un ejemplo simple pero característico del lenguaje ensamblador 6502 sería :

MSG: .ASCIIZ "Hello, world!"

LDX #0

LDA MSG,X ; load initial char

@LP: JSR $FFD2 ; chrout

INX

LDA MSG,X

BNE @LP

RTS

Características dudosas

El 6502 es notorio por tener una variedad de instrucciones indocumentadas, que varían de un diseño al siguiente. El decodificado de instrucciones en los 6502 es implementada en un array de lógica hardware (similar a un Programmable Logic Array ) que se define solamente para los opcodes válidos. Los 32 opcodes indocumentados accionan varias instrucciones válidas a la vez, dando resultados inesperados.

La instrucción de salto indirecto en el 6502, JMP (xxxx) , está quebrada. Si la dirección hexadecimal fuera xxFF , el procesador no tendrá acceso a la dirección almacenada en xxFF y xxFF+1 , sino a xxFF y a xx00. Los 6510 no fijaron este bug, ni es fijado en cualquiera de las otras versiones NMOS de los 6502 como los 8502 y el 2A03. Bill Mensch, del Western Design Center es el primero en fijarlo, en la versión 65C02 CMOS; entonces se decidió diseñar el procesador 65C816 , un sucesor 16-bit del 65C02.

Anecdotario 6502

|

||||||||

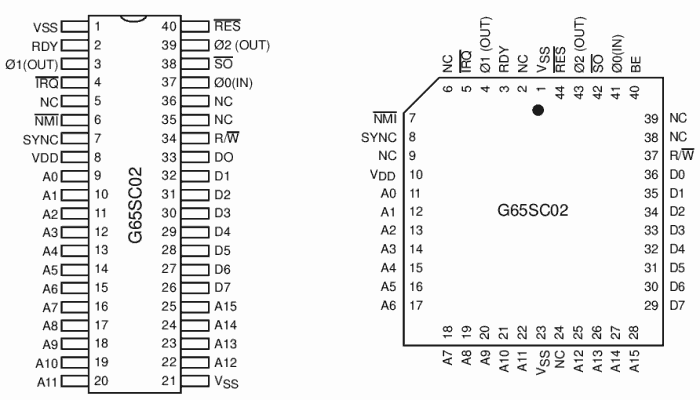

| Pin | Nombre | Dir | Descripción | Pin | Nombre | Dir | Descripción | |

|---|---|---|---|---|---|---|---|---|

| 1 | VSS | Masa | 40 | /RES | Reset | |||

| 2 | RDY | Memory ready signal | 39 | 02 | Sync / Clock out | |||

| 3 | 01 | Clock out (02 invertido) | 38 | SO | Set Overflow flag | |||

| 4 | /IRQ | Interrupt request signal | 37 | 00 | Clock in | |||

| 5 | NC | No conectado | 36 | NC | No conectado | |||

| 6 | /NMI | Interrupcion no enmascarable | 35 | NC | No conectado | |||

| 7 | SYNC | 34 | R//W | |||||

| 8 | Vdd | Alimentación | 33 | D0 | Data Bus 0 | |||

| 9 | A0 | Adress Bus 0 | 32 | D1 | Data Bus 1 | |||

| 10 | A1 | Adress Bus 1 | 31 | D2 | Data Bus 2 | |||

| 11 | A2 | Adress Bus 2 | 30 | D3 | Data Bus 3 | |||

| 12 | A3 | Adress Bus 3 | 29 | D4 | Data Bus 4 | |||

| 13 | A4 | Adress Bus 4 | 28 | D5 | Data Bus 5 | |||

| 14 | A5 | Adress Bus 5 | 27 | D6 | Data Bus 6 | |||

| 15 | A6 | Adress Bus 6 | 26 | D7 | Data Bus 7 | |||

| 16 | A7 | Adress Bus 7 | 25 | A15 | Adress Bus 15 | |||

| 17 | A8 | Adress Bus 8 | 24 | A14 | Adress Bus 14 | |||

| 18 | A9 | Adress Bus 9 | 23 | A13 | Adress Bus 13 | |||

| 19 | A10 | Adress Bus 10 | 22 | A12 | Adress Bus 12 | |||

| 20 | A11 | Adress Bus 11 | 21 | VSS | Masa | |||

Zilog Z80 : una de las CPU de 8 bits que ha sobrevivido hasta hoy por su versatilidad. Unos ingenieros de Intel se separan en 1977 de la empresa y fundan Zilog, desarrollando un chip compatible con el I8080 (entonces dominador del mercado con CP/M) pero mejorado. Su uso se generaliza y arrebata a Intel el mercado de 8 bits. Se implementa en ordenadores, consolas, handhelds, sistemas GPS, videos, modems, tarjetas PC (SCSI, modem,...), lectores de tarjetas, centralitas, ACDs,...

Se comercializan 5 versiones: Z80 (2'5 Mhz), Z80A (4 Mhz), Z80B (6 Mhz), Z80C (5 Mhz), que se diferencian por la velocidad maxima soportada.

Le sucede la serie Z08400x (NMOS a 4, 6'17 y 8 Mhz) y Z84C00xx (CMOS a 06'17, 08,10 y 12 Mhz)

Tiene varios clones como el NEC D780C (Zilog licencia la tecnologia a terceros: la LR35902, CPU de la Nintendo Gameboy, tiene un corazon Z80)

Los programadores en assambler Z80 son los que lo tienen mas sencillo al saltar al ASM x86 del PC.

Tiene descendientes de 16 bits (Z8000) y de 32 bits (Z380) que se montan en raros casos en ordenadores y consolas, pero que siguen encontrandose en otros campos.

El Z80 tiene un bus de datos de 8 bits (D0 a D7), un bus de direcciones de 16 bits (A0 a A15, que le permite direccionar hasta 216 = 64 Kb), 8 Registros Principales de 8 bits (A,B,C,D,E,H,L,F), 8 Registros Alternativos de 8 bits (A',B',C',D',E',H',L',F'), 4 registros de 16 bits (SP o Stac Pointer, PC o Program Counter, IX, IY o registros de indices) y dos de 8 bits (I o Interupt, R o Refresh)

Se alimenta con 5V ± 5 %, con un consumo de 150 mA (Z80) o de 200 mA (Z80A)

| Pin | Nombre | Dir | Descripción | CONECTOR | Pin | Nombre | Dir | Descripción |

|---|---|---|---|---|---|---|---|---|

| 1 | A11 | Adress Bus 11 |  |

40 | A10 | Adress Bus 10 | ||

| 2 | A12 | Adress Bus 12 | 39 | A9 | Adress Bus 9 | |||

| 3 | A13 | Adress Bus 13 | 38 | A8 | Adress Bus 8 | |||

| 4 | A14 | Adress Bus 14 | 37 | A7 | Adress Bus 7 | |||

| 5 | A15 | Adress Bus 15 | 36 | A6 | Adress Bus 6 | |||

| 6 | 0 | Reloj | 35 | A5 | Adress Bus 5 | |||

| 7 | D4 | Data Bus 4 | 34 | A4 | Adress Bus 4 | |||

| 8 | D3 | Data Bus 3 | 33 | A3 | Adress Bus 3 | |||

| 9 | D5 | Data Bus 5 | 32 | A2 | Adress Bus 2 | |||

| 10 | D6 | Data Bus 6 | 31 | A1 | Adress Bus 1 | |||

| 11 | +5V | Alimentacion | 30 | A0 | Adress Bus 0 | |||

| 12 | D2 | Data Bus 2 | 29 | GND | Masa | |||

| 13 | D7 | Data Bus 7 | 28 | /RFSH | Refresh | |||

| 14 | D0 | Data Bus 0 | 27 | M1 | Machine Cicle 1 | |||

| 15 | D1 | Data Bus 17 | 26 | /RESET | Reset | |||

| 16 | /INT | Interrupcion enmascarable | 25 | /BUSRQ | Bus Request | |||

| 17 | /NMI | Interrupcion no enmascarable | 24 | /WAIT | Wait | |||

| 18 | /HALT | Halt State | 23 | /BUSAK | Bus Acknowlegde | |||

| 19 | /MREQ | Memory Request | 22 | /WR | Write | |||

| 20 | /IORQ | Input/Output Request | 21 | /RD | Read |

El siguiente microprocesador creado por la empresa Intel fue el 8085 en 1977. La alimentación es única: requiere sólo +5V. Esto se debe a la nueva tecnología utilizada para la fabricación llamada HMOS (High performance N-channel MOS) que además permite una mayor integración, llegando a la VLSI (Very Large Scale of Integration o muy alta escala de integración) con más de diez mil transistores (el 8085 no es VLSI, pero sí el 8088).

Tiene incorporado el generador de pulsos de reloj con lo que sólo hace falta un cristal de cuarzo y un par de capacitores externos (para el 8080 se necesitaba el circuito integrado auxiliar que lleva el código 8224). Además está mejorado en lo que se refiere a las interrupciones. Incluye las 74 instrucciones del 8080 y posee dos adicionales (RIM y SIM) referidas a este sistema de interrupciones y a la entrada y salida serie. El bus de datos está multiplexado con los ocho bits menos significativos del bus de direcciones (utiliza los mismos pines para ambos buses), con lo que permite tener más pines libres para el bus de control del microprocesador (el 8080 necesitaba un integrado especial, el 8228, para generar el bus de control).

Intel produjo ROMs, RAMs y chips de soporte que tienen también el bus multiplexado de la misma manera que el microprocesador. Todos estos integrados forman la familia MCS-85.

Debido a la gran densidad de integración comparado con el 8080, se utilizó mucho este microprocesador en aplicaciones industriales. Sin embargo, para uso general (ordenadores, consolas, periféricos, control de TV y videos, máquinas vending, incluso modems) es el Zilog Z80 el claro vencedor.

No obstante, y al contar con la ventaja de un modelo CMOS (el 80C85, de consumo reducido) consigue un nicho en los ordenadores Handheld, equipando al Tandy 100, Casio FP-200...).

Asimismo su resistencia a radiaciones hace que se emplee en los campos militar (uno de sus clones soviéticos es sólo para uso militar) y espacial (el robot explorador de Marte Sojurner tiene un 80C85 de CPU)

Interrupciones Posee un complejo y completo sistema de interrupciones, con 5 terminales destinados al tratamiento de interrupciones y 3 formas diferentes de tratar las interrupciones. Los nombres de estos cinco terminales son:

Estas interrupciones se pueden habilitar o deshabilitar mediante las instrucciones EI y DI, como en el caso de INTR; pero además son enmascarables por software mediante la instrucción SIM (Set Interrupt Mask). Es posible leer tanto el estado de la máscara como las interrupciones que se han producido y aún no se atendieron mediante la instrucción RIM.

| Nivel de prioridad | Nombre de la interrupción | Valor leído en el bus de datos | Dirección Hex de la subrutina |

|---|---|---|---|

| Mayor prioridad | TRAP | No importa | 0024 |

| - | RST 7.5 | 003C | |

| - | RST 6.5 | 0034 | |

| - | RST 5.5 | 002C | |

| Menor prioridad | INTR | 11000111 | 0000 |

| 11001111 | 0008 | ||

| 11010111 | 0010 | ||

| 11011111 | 0018 | ||

| 11100111 | 0020 | ||

| 11101111 | 0028 | ||

| 11110111 | 0030 | ||

| 11111111 | 0038 |

Control de entrada/salida serie Este microprocesador posee dos terminales denominados SID (Serial Input Data) y SOD (Serial Output Data). Estos terminales se pueden usar con propósitos generales. Por ejemplo el terminal SID se puede conectar a un interruptor y el SOD a un LED (a través de una compuerta inversora externa). Para leer el estado del terminal SID se ejecuta la instrucción RIM, con lo que se puede leer en el bit 7 del acumulador el estado de dicho terminal.

Para enviar un dato por el terminal SOD se ejecuta la instrucción SIM, donde el bit 7 del acumulador debe tener el valor a poner en el terminal, y el bit 6 debe estar a uno.

Conjunto de instrucciones del 8085 Aparte de las 74 instrucciones del 8080, este procesador posee dos instrucciones más.

Estos datos deben estar cargados en el acumulador y son:

Luego de la ejecución de esta instrucción, el acumulador tiene lo siguiente:

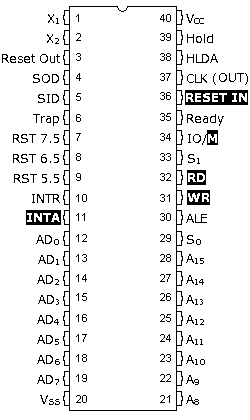

| Pin | Nombre | Dir | Descripción | CONECTOR | Pin | Nombre | Dir | Descripción |

|---|---|---|---|---|---|---|---|---|

| 1 | X1 | Oscilador de cuarzo 1 |  |

40 | VCC +5v | Alimentacion | ||

| 2 | X2 | Oscilador de cuarzo 1 | 39 | HOLD | Sirve para poner los buses en alta impedancia para el manejo de DMA | |||

| 12 | AD0 | Adress/Data Bus 0 | 26 | SO | Bit de estado del 8085 | |||

| 13 | AD1 | Adress/Data Bus 1 | 28 | A15 | Adress Bus 15 | |||

| 14 | AD2 | Adress/Data Bus 2 | 27 | A14 | Adress Bus 14 | |||

| 15 | AD3 | Adress/Data Bus 3 | 26 | A13 | Adress Bus 13 | |||

| 16 | AD4 | Adress/Data Bus 4 | 25 | A12 | Adress Bus 12 | |||

| 17 | AD5 | Adress/Data Bus 5 | 24 | A11 | Adress Bus 11 | |||

| 18 | AD6 | Adress/Data Bus 6 | 23 | A10 | Adress Bus 10 | |||

| 19 | AD7 | Adress/Data Bus 7 | 22 | A9 | Adress Bus 9 | |||

| 20 | GND | Masa | 21 | A8 | Adress Bus 8 |

| 8085 | 80C85 |

|---|---|

|

| |

El 6809 es un microprocesador de 8 bits fabricado por Motorola, desde 1979. El 6809 fue un avance mayor sobre sus dos predecesores, el Motorola 6800 y el MOS Technology 6502. Es considerado como el precursor moral de la familia de procesadores Motorola 68000 , aunque el diseño del 68K actualmente se sobrepasa al proyecto 6809.

Entre las mejoras más significativas que el 6809 introdujo sobre sus predecesores fue el empleo de dos acumuladores de 8 bits, mejor que uno en el 6502, el cual puede ser combinado en un único registro de 16 bits. También tenía dos registros índice de 16 bits (frente a los 8 bits del 6502) y dos punteros de pila (frente a uno en el 6502), permitiendo modos de direccionamiento bastante avanzados.

El 6809 es compatible a nivel de código fuente con el 6800, aunque el 6800 tenía 78 instrucciones y el 6809 solo 59. Algunas instrucciones fueron reemplazadas por otras más generales que el ensamblador podía traducir, y algunas donde reemplazadas por modos de direccionamiento. El conjunto de instrucciones y complemento de registro fue altamente ortogonal, haciendo la programación en lenguaje ensamblador bastante agradable, y no la pesadilla de la mayoría de otros CPUs de microcomputadoras de la época.

Otra característica fue una de las primeras instrucciones de multiplicación de su tiempo, aritmética de 16 bits y una interrupción rápida especial. Pero el 6809 fue también altamente optimizado, con una velocidad hasta 5 veces superior a las CPUs de la serie 6800. Al igual que el 6800, incluyó la tristemente célebre e indocumentada instrucción de prueba de bus Halt and Catch Fire (HCF) (detener e incendiarse).

La optimización del procesador 6809 significó que, a diferencia de muchos procesadores de aquel entonces, las instrucciones fueron en su mayoría construidas dentro del procesador, en lugar de ser escritas utilizando microcódigo o microprogramación. Esto significó que podía tomar muchos menos ciclos de reloj de CPU para procesar las instrucciones. Como ejemplo, la instrucción "ADDA 63" toma tres ciclos de reloj (dos para recoger la instrucción, y una para que tuviera lugar la operación).

En el Zilog Z80, el cual fue probablemente el principal competidor al 6809, "ADD A,63" toma siete ciclos de reloj. Esto significa que el Z80 necesita una velocidad de reloj de al menos el doble que un 6809 para igualar su rendimiento. En adición, las CPUs de 8 bits de Motorola usaban un ciclo de reloj por acceso a memoria, no el reloj de estado de la mayoría de los otros microcomputadores del esa época. Una simple operación de lectura de memoria en un Z-80, por ejemplo, necesita varios ciclos de reloj frente al único ciclo de reloj del 6800/6809. ¡Distintos relojes!

El Motorola 6809 se produjo en tres versiones, a 1 MHz, 1,5 Mhz y 2 MHz, que se indicaban con una letra entre la pareja de dígitos 68 y 09 (A 1,5; B 2 Mhz). Un primer sufijo indicaba si el generador de reloj era interno o externo (E). Un segundo sufijo indicaba si el rango de funcionamiento era de 0 °C a 70 °C (ninguno) o de -40 °C a 85 °C (C). Y un tercero indicaba si el encapsulado era plástico (P) o cerámico (S también llamado cerdip)

El 6809 tiene un generador de reloj interno (sólo necesita un cristal externo) mientras que el 6809E necesita además un generador de reloj externo. Debido a ello, los pines 39 (TSC / XTAL), 38 (LIC / EXTAL), 36 (AVMA / !MRDY) y 33 (BUSY / !DMA/!BREQ) son diferentes en los 6809E / 6809.

Fuente : Wikipedia

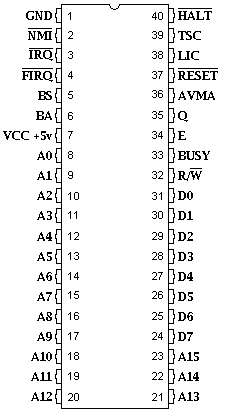

| Pin | Nombre | Dir | Descripción | CONECTOR | Pin | Nombre | Dir | Descripción |

|---|---|---|---|---|---|---|---|---|

| 1 | GND | Masa |  |

40 | /HALT | Halt State | ||

| 2 | /NMI | Interrupcion no enmascarable | 39 | TSC | ||||

| 3 | /IRQ | Interrupt request signal | 38 | LIC | ||||

| 4 | /FIRQ | 37 | /RESET | Reset | ||||

| 5 | AVMA | 36 | BS | |||||

| 6 | BA | 35 | Q | |||||

| 7 | VCC +5v | Alimentacion | 34 | E | ||||

| 8 | A0 | Adress Bus 0 | 33 | BUSY | ||||

| 9 | A1 | Adress Bus 1 | 32 | R//W | ||||

| 10 | A2 | Adress Bus 2 | 31 | D0 | Data Bus 0 | |||

| 11 | A3 | Adress Bus 3 | 30 | D1 | Data Bus 1 | |||

| 12 | A4 | Adress Bus 1 | 29 | D2 | Data Bus 2 | |||

| 13 | A5 | Adress Bus 5 | 28 | D3 | Data Bus 3 | |||

| 14 | A6 | Adress Bus 6 | 27 | D4 | Data Bus 4 | |||

| 15 | A7 | Adress Bus 7 | 26 | D5 | Data Bus 5 | |||

| 16 | A8 | Adress Bus 8 | 25 | D6 | Data Bus 6 | |||

| 17 | A9 | Adress Bus 9 | 24 | D7 | Data Bus 7 | |||

| 18 | A10 | Adress Bus 10 | 23 | A15 | Adress Bus 15 | |||

| 19 | A11 | Adress Bus 11 | 22 | A14 | Adress Bus 14 | |||

| 20 | A12 | Adress Bus 12 | 21 | A13 | Adress Bus 13 |

Motorola MC 68000 : el gran competidor de los chips Intel 286/386 al equipar al 80% de los ordenadores no PC y a parte de las consolas y recreativas.

El Motorola 68000 es un microprocesador CISC 16/32 -bit diseñado y comercializado por Motorola (actualmente producido por Freescale). Introducido en 1979, con la tecnología HMOS, fue el primer miembro de la exitosa familia de microprocesadores m68k de 32 bits, por lo general el software creado para este procesador es compatible con las versiones futuras del resto de la línea a pesar de que esta primera versión está limitada a un ancho de bus externo de 16-bit. Después de tres décadas en la producción, la arquitectura 68000 todavía está en uso.

El Motorola 68000 (MC68000), debe su nombre al número de transistores de los que se compone, este microprocesador ha sido utilizado, entre otros, en los Commodore Amiga, los Atari ST, los primeros Macintosh, en Sharp X68000 y las primeras PCB de videojuegos de recreativas de Capcom. El MC68000 fue lanzado al mercado en 1980 y es el primero de una familia de microprocesadores que está formada por el Motorola 68010, Motorola 68020, Motorola 68030, Motorola 68040 y el Motorola 68060. Esta familia de procesadores a menudo es designada por el término genérico 680x0, m68k, 68k o familia 68000. Motorola desarrolló también a un sucesor de los 680x0: el Coldfire.

| Pin | Nombre | Dir | Descripción | CONECTOR | Pin | Nombre | Dir | Descripción |

|---|---|---|---|---|---|---|---|---|

| 1 | D4 | Data Bus 4 |  |

33 | A 5 | Adress Bus 5 | ||

| 2 | D 3 | Data Bus 3 | 34 | A 6 | Adress Bus 6 | |||

| 3 | D 2 | Data Bus 2 | 35 | A 7 | Adress Bus 7 | |||

| 4 | D 1 | Data Bus 1 | 36 | A 8 | Adress Bus 8 | |||

| 5 | D 0 | Data Bus 0 | 37 | A 9 | Adress Bus 9 | |||

| 6 | /AS | 38 | A 10 | Adress Bus 10 | ||||

| 7 | /UDS | 39 | A 11 | Adress Bus 11 | ||||

| 8 | /LDS | 40 | A 12 | Adress Bus 12 | ||||

| 9 | /R-W | 41 | A 13 | Adress Bus 13 | ||||

| 10 | /DTACK | 42 | A 14 | Adress Bus 14 | ||||

| 11 | /BG | 43 | A 15 | Adress Bus 15 | ||||

| 12 | /BGACK | 44 | A 16 | Adress Bus 16 | ||||

| 13 | /BR | 45 | A 17 | Adress Bus 17 | ||||

| 14 | + 5V | Alimentación | 46 | A 18 | Adress Bus 18 | |||

| 15 | CLK | Reloj | 47 | A 19 | Adress Bus 19 | |||

| 16 | GND | Masa | 48 | A 20 | Adress Bus 20 | |||

| 17 | /HALT | 49 | + 5V | Alimentación | ||||

| 18 | /RESET | Reset | 50 | A 21 | Adress Bus 21 | |||

| 19 | /VMA | 51 | A 22 | Adress Bus 22 | ||||

| 20 | E | 52 | A 23 | Adress Bus 23 | ||||

| 21 | /VPA | 53 | GND | Masa | ||||

| 22 | /BERR | 54 | D 15 | Data Bus 15 | ||||

| 23 | /IPL 2 | 55 | D 14 | Data Bus 14 | ||||

| 24 | /IPL 1 | 56 | D 13 | Data Bus 13 | ||||

| 25 | /IPL 0 | 57 | D 12 | Data Bus 12 | ||||

| 26 | FC 2 | 58 | D 11 | Data Bus 11 | ||||

| 27 | FC 1 | 59 | D 10 | Data Bus 10 | ||||

| 28 | FC 0 | 60 | D 9 | Data Bus 9 | ||||

| 29 | A 1 | Adress Bus 1 | 61 | D 8 | Data Bus 8 | |||

| 30 | A 2 | Adress Bus 2 | 62 | D 7 | Data Bus 7 | |||

| 31 | A 3 | Adress Bus 3 | 63 | D 6 | Data Bus 6 | |||

| 32 | A 4 | Adress Bus 4 | 64 | D 5 | Data Bus 5 |

| Sobre CPUs en general | Específicas de una CPU o familia | Genéricas |

|---|---|---|

|

|

| |

© Miguel Durán 1996 - con licencia